# **G**LOBAL **J**OURNAL OF **E**NGINEERING **S**CIENCE AND **R**ESEARCHES

# DESIGN AND SIMULATION OF CASCADED SEVEN LEVEL H-BRIDGE MULTILEVEL INVERTER BASED DSTATCOM FOR POWER QYALITY IMPROVEMENT

# **Prof. Suryakant H. Pawar<sup>\*1</sup> and Chetan A. Jambhulkar<sup>2</sup>**

\*1Associate Professor, Department of Electrical Engineering, Government College of Engineering, Karad, Maharashtra,

India

# <sup>2</sup>P. G. Student, Department of Electrical Engineering, Government College of Engineering, Karad, Maharashtra, India

ABSTRACT

In this paper the design of a DSTATCOM employing a Seven–Level Cascaded H-Bridge Multilevel Inverter (CHBMLI) in medium voltage distribution power system is presented. The DSTATCOM helps to improve sending end & receiving end voltage and current drawn from a Non Linear Load (NLL). The control strategy based on Synchronous Reference Frame (SRF) theory is designed so that the voltage injected by active filter is able to mitigate the voltage sag, imbalance in the source voltage and reduce the harmonic content. The Level Shifted PWM (LSPWM) techniques are adopted to investigate the performance of CHB inverter. The performance of the proposed DSTATCOM is validated through simulation using MATLAB software with its SIMULINK and Power System block set tool and also performance of the system without DSTATCOM and with DSTATCOM is evaluated.

**Keywords**— DSTATCOM, Level Shifted Pulse Width Modulation (LSPWM), Cascaded H-Bridge Multilevel Inverter (CHBMLI), MOSFET.

# I. INTRODUCTION

In recent years Electrical Power Quality had obtained more attention in power engineering. In present day's power distribution systems is suffering from severe power quality problems. These power quality problems include high reactive power burden, harmonics currents, load unbalance, excessive neutral current etc. The measure of power quality depends upon the needs of the equipment that is being supplied. Usually the term power quality refers to maintaining a sinusoidal waveform of bus voltages at rated voltage and frequency [1]. The waveform of electric power at generation stage is purely sinusoidal and free from any distortion. Many of the Power conversion and consumption equipment are also designed to function under pure sinusoidal voltage waveforms. However, there are many devices that distort the waveform. These distortions may propagate all over the electrical network. In recent years, there has been an increased use of non-linear loads which has resulted in an increased fraction of non-sinusoidal currents and voltages in Electric Network. The wave shape phenomena associated with power quality may be characterized into synchronous and non synchronous phenomena. Synchronous phenomena refer to those in synchronism with A.C waveform at power frequency [10], [13].

A group of controllers together called Custom Power Devices (CPD), which include the DSTATCOM (distribution static compensator), The DSTATCOM, is a shunt-connected device, which takes care of the power quality problems in the currents it consists of a dc capacitor, three-phase inverter (IGBT, MOSFET) module, ac filter, coupling transformer and a control strategy. The basic electronic block of the D-STATCOM is the voltage-sourced inverter that converts an input dc voltage into a three-phase output voltage at fundamental frequency. The D-STACOM employs an inverter to convert the DC link voltage Vdc on the capacitor to a voltage source of adjustable magnitude and phase. Therefore the D-STATCOM can be treated as a voltage controlled source. The D-STATCOM can also be seen as a current-controlled source. The DSTATCOM is based on the instantaneous real-power theory; it provides good compensation characteristics in steady state as well as transient states [9]. The instantaneous real-power theory generates the reference currents required to compensate the distorted line current harmonics and reactive power. It also tries to maintain the dc-bus voltage across the capacitor constant.

A multilevel inverter can reduce the device voltage and the output harmonics by increasing the number of output voltage levels. There are several types of multilevel inverters: cascaded H-bridge (CHB), neutral point clamped, flying capacitor [5], [6], [8], [11]. In particular, among these topologies, CHB inverters are being widely used because of their modularity and simplicity. Various modulation methods can be applied to CHB inverters. CHB inverters can also increase the number of output voltage levels easily by increasing the number of H-bridges. This paper presents a DSTATCOM with a proportional integral controller based CHB multilevel (seven level) inverter for the harmonics and reactive power mitigation of the nonlinear loads. This type of arrangements have been widely used for PQ applications due to increase in the number of voltage levels, low switching losses, low electromagnetic compatibility for hybrid filters and higher order harmonic elimination.

#### II. DISTRIBUTED STATIC SYNCHRONOUS COMPENSATOR (DSTATCOM) A. Basic Configuration of DSTATCOM

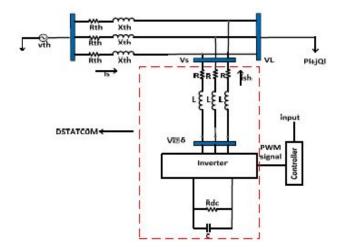

The DSTATCOM is a voltage or current source inverter based custom power device connected in shunt with the power system. It is connected near the load at the distribution systems [12], [14]. The basic structure of DSTATCOM is presented in Figure 2.1 As shown in Figure 2.1; DSTATCOM consists of an inverter, dc link capacitance C that providing the dc voltage for inverter, coupling inductance L used for current filter and reactive power exchange between DSTATCOM and power system and a control unit to generate PWM signals for the switches of inverter. In Figure 4, and R respectively represent switching losses in inverter and winding resistance of coupling inductance [6].

Figure 2.1 - Basic structure of DSTATCOM in distribution system

#### **B.** Cascaded H-Bridge Inverter Topologies

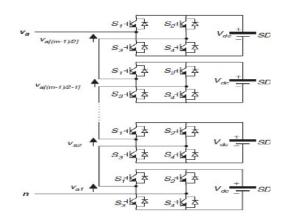

The N-level cascaded H-bridge, multilevel inverter comprises series connected single phase H-bridges per phase, for which each H-bridge has its own isolated dc source. Figure 2.2 shows one phase of an n-level cascaded H-bridge inverter. The cascaded H-bridge multilevel inverter is based on multiple two level inverter outputs (each H-bridge), with the output of each phase shifted. Despite four diodes and switches, it achieves the greatest number of output voltage levels for the fewest switches. Its main limitation lies in its need for isolated power sources for each level and for each phase, although for VA compensation, capacitors replace the dc supplies, and the necessary capacitor energy is only to replace losses due to inverter losses. Its modular structure of identical H-bridges is a positive feature.

31

## [Pawar, 2(2): February 2015]

#### Figure 2.2 - Single-Phase Structure of a Multilevel Cascaded H-Bridge Inverter

- The number of levels in the line-to-line voltage waveform will be k=2N-1,

- While the number of levels in the line to neutral of a star (wye) load will be p = 2k 1

- The number of capacitors or isolated supplies required per phase is  $Ncap = \frac{1}{2}(N-1)$

- The number of possible switch states is nstates = N phases

- The number of switches in each leg is Sn = 2(N-1)

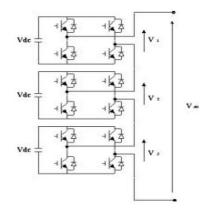

Figure 2.3 shows the seven level multilevel inverter and. Here even though we have twelve switches at any switching state only two switches are on/off at a voltage level of Vdc/3, so switching losses are reduced. In three level inverter dv/dt is Vdc, but in five level inverter dv/dt is Vdc/2 and in seven level inverter dv/dt is Vdc/3. As dv/dt reduces, the stress on switches reduces and EMI also reduces.

Figure 2.3 - Block diagram of 7-level CHB inverter model

## **III. REFERENCE CURRENT CONTROL STRATEGY**

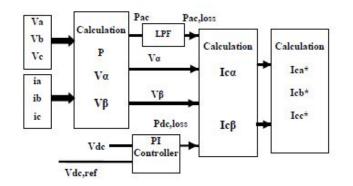

The control scheme of the shunt active power filter must calculate the current reference signals from each phase of the inverter using instantaneous real-power compensator. The block diagram as shown in Figure 3, that control scheme generates the reference current required to compensate the load current harmonics and reactive power. The PI controller is tried to maintain the dc-bus voltage across the capacitor constant of the cascaded inverter. This instantaneous real-power compensator with PI-controller is used to extracts reference value of current to be compensated.

32

Figure 3: Reference current generator using instantaneous real-power theory

These reference currents isa\*, isb \*and isc \* are calculated instantaneously without any time delay by using the instantaneous  $\alpha,\beta$  coordinate currents. The required references current derivate from the inverse Clarke transformation and it can be written as

$$\begin{bmatrix} i_{sa} \\ i_{sb} \\ i_{sc} \end{bmatrix} = \sqrt{2/3} \begin{bmatrix} 1 & 0 \\ -1/2 & \sqrt{3/2} \\ -1/2 & -\sqrt{3/2} \end{bmatrix} \begin{bmatrix} i_{c\alpha} \\ i_{c\beta} \end{bmatrix}$$

The p-q theory performs a Clarke transformation of a stationary system of coordinates a b c to an orthogonal reference system of coordinates  $\alpha,\beta$ . In a b c coordinates axes are fixed on the same plane, apart from each other by 120 that as shown in Fig 5. The instantaneous space vectors voltage and current Va , ia are set on the a axis, Vb , ib are on the b axis, and Vc , ic are on the c axis. These space vectors are easily transformed into  $\alpha,\beta$  coordinates. The instantaneous source voltages vsa, vsb, vsc are transformed into  $\alpha,\beta$  coordinate's voltage by Clarke transformation as follows:

$$v_{\alpha\beta0} = \sqrt{2/3} \begin{bmatrix} 1 & -1/2 & -1/2 \\ 0 & \sqrt{3/2} & -\sqrt{3/2} \\ 1/\sqrt{2} & 1/\sqrt{2} & 1/\sqrt{2} \end{bmatrix} v_{abc}$$

Similarly, the instantaneous source current isa, isb, isc also transformed into  $\alpha$ ,  $\beta$  coordinate's current by Clarke transformation that is given as

$$i_{\alpha\beta0} = \sqrt{2/3} \begin{bmatrix} 1 & -1/2 & -1/2 \\ 0 & \sqrt{3/2} & -\sqrt{3/2} \\ 1/\sqrt{2} & 1/\sqrt{2} & 1/\sqrt{2} \end{bmatrix} i_{\alphabc}$$

Where  $\alpha$  and  $\beta$  axes are the orthogonal coordinates. They V $\alpha$ , i $\alpha$  are on the  $\alpha$ -axis, and V $\beta$ , i $\beta$  are on the  $\beta$ -axis. The reference currents isa\*, isb \* and isc \* are compared with actual source current isa , isb and isc that facilitates generating cascaded multilevel inverter switching signals using the proposed triangular-sampling current modulator. The small amount of real-power is adjusted by changing the amplitude of fundamental component of reference currents and the objective of this algorithm is to compensate all undesirable components. When the power system voltages are balanced and sinusoidal, it leads to constant power at the dc bus capacitor and balanced sinusoidal currents at AC mains simultaneously.

33

#### **IV. PWM TECHNIQUES FOR CHB INVERTER**

# [Pawar, 2(2): February 2015]

#### ISSN 2348 - 8034

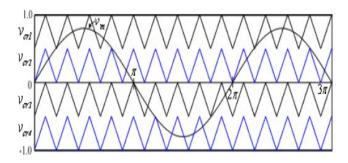

The most popular PWM techniques for CHB inverter are 1.Phase Shifted Carrier PWM (PSCPWM), 2.Level Shifted Carrier PWM (LSCPWM).

#### Figure 4: Level Shifted Carrier PWM (LSCPWM)

Each cell is modulated independently using sinusoidal unipolar pulse width modulation and bipolar pulse width modulation respectively, providing an even power distribution among the cells. A carrier level shifted by 1/m (No. of levels) for cascaded inverter is introduced across the cells to generate the stepped multilevel output waveform with lower distortion.

## V. MATLAB/SIMULINK MODELING AND SIMULATION RESULTS

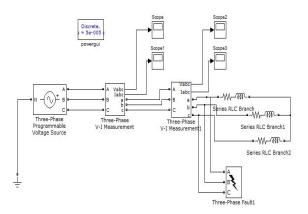

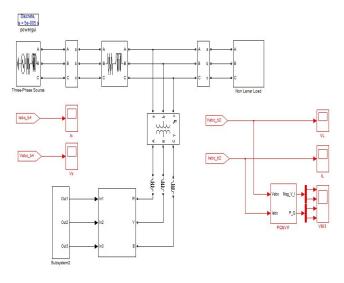

Figure 5.1 and 5.6 shows the MATLAB/SIMULINK power circuit model of DSTATCOM. It consists of four blocks named as source block, nonlinear load block, control block, measurement block. The system parameters for simulation study are source voltage of 11 KV, 50 Hz AC supply, Inverter series inductance 10 mH, Source resistance of 0.1 ohm and inductance of 0.9 mH. Load resistance and inductance are chosen as 60ohm and 30 mH respectively.

#### A) Without compensation

#### Fig.5.1 SIMULINK model without DSTATCOM

In this model a three phase source of 11 KV is connected to non linear load. When this is connected to the source a dip in voltage called sag occurs. Due to the sag the voltage will get increased. Without compensation means no compensating device is connected to compensate the voltage sag. This dip in voltage is the pollution caused by the non linear loads.

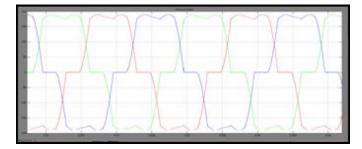

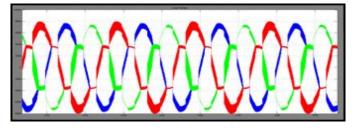

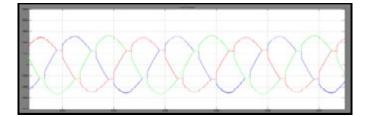

Figure 5.2: Source Current without DSTATCOM

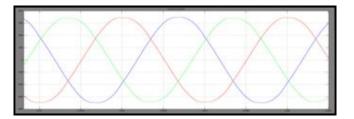

Figure 5.3: Source Voltage without DSTATCOM

Figure 5.4: Load Current without DSTATCOM

Figure 5.5: Load Current without DSTATCOM

B) With compensation

Fig.5.6 SIMULINK model with DSTATCOM

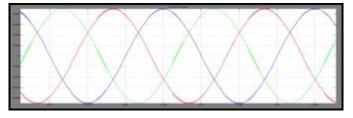

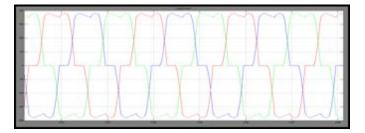

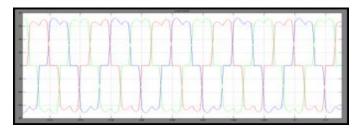

Figure 5.7: Source Current with DSTATCOM

Figure 5.8: Source Voltage with DSTATCOM

Figure 5.9: Load Current without DSTATCOM

36

#### Figure 5.10: Load Current with DSTATCOM

#### **VI. CONCLUSION**

A model of system feeding nonlinear loads has been developed using MATLAB SIMULINK. DSTATCOM with Cascaded H-bridge Inverter is investigated. The cascaded H-bridge multilevel boost inverter without inductors uses a standard three-leg inverter (one leg for each phase) and an H-bridge in series with each inverter leg. The load voltage, RMS

Voltage, current, real power, reactive power under nonlinear loads is simulated. From the results it is seen that there is an improvement in power factor. Finally, the performance of the system without DSTATCOM and with DSTATCOM using CHB is evaluated.

#### REFERENCES

- 1. Bhim Singh, Kamal Al-Haddad & Ambrish Chandra, "A New Control Approach to 3-phase Active Filter for Harmonics and Reactive Power Compensation"-IEEE Trans. on Power Systems, Vol. 46, NO. 5, pp.133 138, Oct-1999

- 2. Dugan R. C. McGranaghan M. F. and Beaty H. W. "Electric Power Systems Quality," McGraw-Hill, 1996

- 3. G.F. Reed, M. Takeda, and I. lyoda, —Improved power quality solution using advanced solid-slate switching and static compensation technologies, IEEE Power Engineering Society winter Meeting, New York, NY, USA, vol. 2, pp. 1132-1137, 1999.

- 4. J. Ganesh Prasad Reddy, K. Ramesh Reddy, "Design and Simulation of Cascaded H-Bridge Multilevel Inverter Based DSTATCOM for Compensation of Reactive Power and Harmonics", IEEE 1<sup>ST</sup> International Conference on Recent Advances in Information Technology [RAIT]-2012.

- 5. J. Rodriguez, J. S. Lai, and F. Z. Peng, "Multilevel inverters: a survey of topologies, controls, and applications," IEEE Trans. on Industrial Electronics, vol. 49, no. 4, pp. 724-738,2002.

- 6. J. S. Lai and F. Z. Peng, "Multilevel converters- a new breed of power converters," IEEE Trans. on Industry Applications, vol. 32, no. 3, pp. 509-517, 1996.

- 7. Karuppanan P and Kamala Kanta Mahapatra "Shunt Active Power Line Conditioners for Compensating Harmonics and Reactive Power"-Proceedings of the International Conference on Environment and Electrical Engineering (EEEIC), pp.277 – 280, May 2010

- 8. Keith Corzine, Yakov Familiant, "A new cascaded multilevel H-bridge drive" IEEE Transactions on Power Electronics, Vol. 17, No. 1, January 2002.

- 9. Leszek S. Czarnecki "Instantaneous Reactive Power p-q Theory and Power Properties of Three-Phase Systems"- IEEE Trans on Power, VOL. 21, NO. 1, pp 362-367, 2006

- 10. N. G. Hingorani and L. Gyugyi, Understanding FACTS, IEEE Press, 2000.

- 11. P. Giroux and G. Sybille, "Modelling & Simulation of a Distribution STATCOM using Simulink Power System Blocksets," 27 annual conf. of IEEE Ind. Electron. Soc., vol. 2, no. 2, pp.990-994, April 2001.

- 12. S. Iyer, A. Ghosh and A. Joshi, "Inverter Topologies for DSTATCOM applications-A Simulation Study," Elect. Power Syst. Res., vol. 75, no.2/3, pp. 161-170, Aug. 2005.

- 13. S. P. Gawande ,S.Khan, M. R. Ramteke, "Voltage Sag Mitigation Using Multilevel Inverter based Distribution Static Compensator (DSTATCOM) in Low Voltage Distribution System" <u>Power Electronics (IICPE), 2012 IEEE 5th India</u> <u>International Conference.</u>

- 14. W. K. Chang, W. M. Grady, Austin, M. J. Samotyj "Meeting IEEE- 519 Harmonic Voltage and Voltage Distortion Constraints with an Active Power Line Conditioner"- IEEE Trans on Power Delivery, Vol.9, No.3, pp.1531-1537, 1994

- 15. Wei-Neng Chang, Jing-Huan Liau, "Development of a Cascaded Multilevel DSTATCOM for Real-Time Load Power Factor Correction", IEEE 2010 International Power Electronics Conference.